### **General Description**

XBLW GT298 is a high voltage, high current dual full-bridge driver designed to accept standard TTL logic levels and drive inductive loads such as relays, solenoids, DC and stepping motors.

#### Features

- OPRINAGCSTULIYSOITAGE UP TO 46 V

- TOTAL DC CURRENT UP TO 4 A

- LOW SATURATION VOLTAGE

- LOGICAL "0" INPUT VOLTAGE UP TO 1.5 V

- THE LOGIC POWER SUPPLY AND DRIVE POWER SUPPLY ARE INDEPENDENT OF EACH OTHER

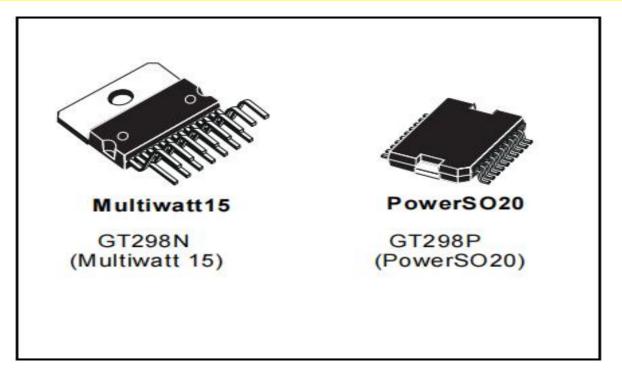

### **Ordering Information**

| Product Model | Package Type | Marking | Packing | Packing Qty |

|---------------|--------------|---------|---------|-------------|

| GT298P        | PowerSO-20   | GT298P  | Таре    | 600PCS/Reel |

| GT298N        | Multiwatt-15 | GT298N  | Tube    | 250PCS/BOX  |

|               |              |         |         |             |

|               |              |         |         |             |

|               |              |         |         |             |

### **Outside View**

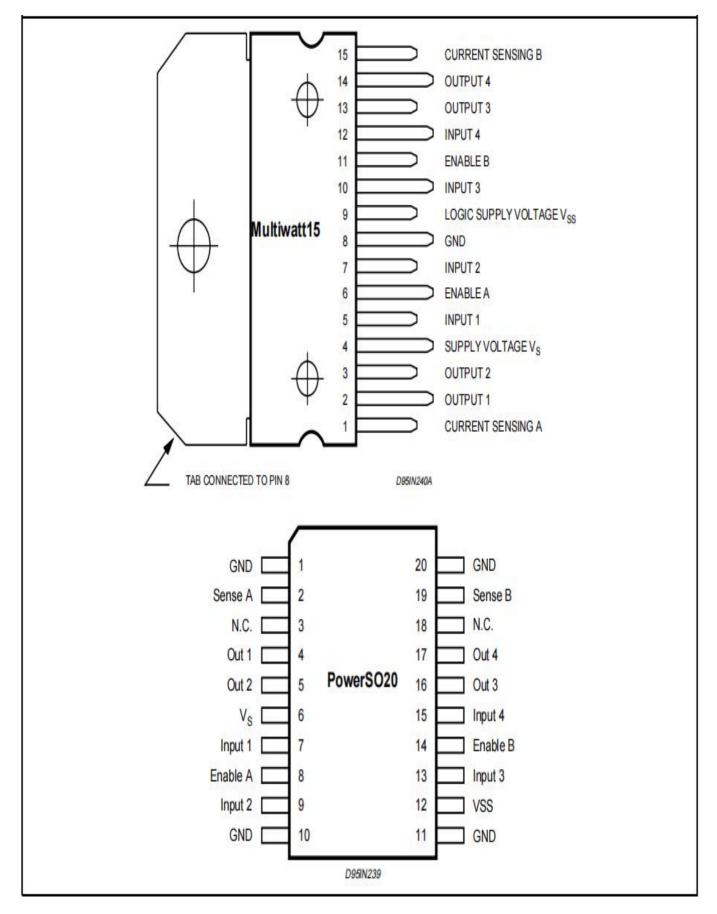

## **Pin Definition And Function**

## **PINS AND DEFINITIONS OF XBLW GT298**

| MW.15  | PowerSO    | Name                                                                                                                                         | Function                                                                                                                   |  |  |  |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1;15   | 2;19       | Sense A; Sense<br>B                                                                                                                          | Between this pin and ground is connected the sense resistor to control the current of the load.                            |  |  |  |

| 2;3    | 4;5        | Out 1; Out 2                                                                                                                                 | Outputs of the Bridge A; the current that flows through the load connected between these two pins is monitored atpin 1.    |  |  |  |

| 4      | 6          | Vs                                                                                                                                           | Supply Voltage for the Power Output Stages.<br>A non-inductive 100nF capacitor must be connected between this pin and grou |  |  |  |

| 5;7    | 7;9        | Input 1; Input 2                                                                                                                             | TTL Compatible Inputs of the Bridge A.                                                                                     |  |  |  |

| 6;11   | 8;14       | EnableA;Enable<br>B                                                                                                                          | TTL Compatible Enable Input: the L state disables the bridge A (enable A) and/or the bridge B (enable B).                  |  |  |  |

| 8      | 1,10,11,20 | GND                                                                                                                                          | Ground.                                                                                                                    |  |  |  |

| 9      | 12         | VSS                                                                                                                                          | Supply Voltage for the Logic Blocks. A100nF capacitor must be connected<br>between this pin and ground.                    |  |  |  |

| 10; 12 | 13;15      |                                                                                                                                              |                                                                                                                            |  |  |  |

| 13; 14 | 16;17      | 16;17Out 3; Out 4Outputs of the Bridge B. The current that flows through the load connected<br>between these two pins is monitored atpin 15. |                                                                                                                            |  |  |  |

|        | 3;18       | N.C.                                                                                                                                         | Not Connected                                                                                                              |  |  |  |

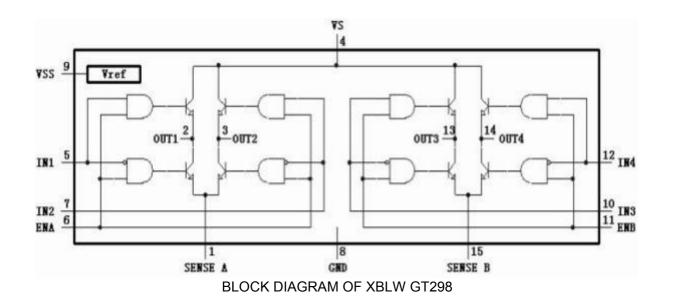

## **Block Diagram**

## ABSOLUTE MAXIMUM RATINGS

| Symbol            | Parameter                                                                                                                        | Value         | Unit        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

| Vs                | Power Supply                                                                                                                     | 50            | V           |

| Vss               | Logic Supply Voltage                                                                                                             | 7             | V           |

| VI,Ven            | Input and Enable Voltage                                                                                                         | –0.3 to 7     | V           |

| lo                | Peak Output Current (each Channel)<br>– Non Repetitive (t = 100µs)<br>–Repetitive (80% on –20% off; ton = 10ms)<br>–DC Operation | 3<br>2.5<br>2 | A<br>A<br>A |

| V <sub>sens</sub> | Sensing Voltage                                                                                                                  | -1 to 2.3     | V           |

| Ptot              | Total Power Dissipation ( $T_{case} = 75$ , C)                                                                                   | 25            | W           |

| Top               | Junction Operating Temperature                                                                                                   | –25 to 130    | ° C         |

| Tstg, Tj          | Storage and Junction Temperature                                                                                                 | -40 to 150    | ° C         |

### **Electrical Characteristics** ( $V_s = 42V$ ; $V_{ss} = 5V$ , $T_j = 25^{\circ}$ C; unless otherwise specified)

| Symbol              |                                                  | Test Conditi                  | ons                    | Min.       | Тур.       | Max.       | Unit     |

|---------------------|--------------------------------------------------|-------------------------------|------------------------|------------|------------|------------|----------|

| Vs                  | Supply Voltage (pin 4)                           | Operative Condition           |                        | V⊮<br>+2.5 |            | 46         | V        |

| Vss                 | Logic Supply Voltage (pin 9)                     |                               |                        | 4.5        | 5          | 7          | V        |

| ls                  | Quiescent Supply Current (pin 4)                 | V <sub>en</sub> = H; I∟ = 0   | $V_i = L$<br>$V_i = H$ |            | 13<br>50   | 22<br>70   | mA<br>mA |

|                     |                                                  | V <sub>en</sub> = L<br>X      | Vi =                   |            |            | 4          | mA       |

| lss                 | Quiescent Current from Vss (pin 9)               | V <sub>en</sub> = H; I∟ = 0   | Vi = L<br>Vi = H       |            | 24<br>7    | 36<br>12   | mA<br>mA |

|                     |                                                  | V <sub>en</sub> = L<br>X      | Vi =                   |            |            | 6          | mA       |

| ViL                 | Input Low Voltage<br>(pins 5, 7, 10, 12)         |                               |                        | -0.3       |            | 1.5        | V        |

| ViH                 | Input High Voltage<br>(pins 5, 7, 10, 12)        |                               |                        | 2.3        |            | VSS        | V        |

| liL                 | Low Voltage Input Current<br>(pins 5, 7, 10, 12) | Vi = L                        |                        |            |            | -10        | μA       |

| Іін                 | High Voltage Input Current (pins 5, 7, 10, 12)   | $Vi = H \le V_{SS} - 0.6V$    |                        |            | 30         | 100        | μA       |

| V <sub>en</sub> = L | Enable Low Voltage (pins 6, 11)                  |                               |                        | -0.3       |            | 1.5        | V        |

| V <sub>en</sub> = H | Enable High Voltage (pins 6, 11)                 |                               |                        | 2.3        |            | Vss        | V        |

| I <sub>en</sub> = L | Low Voltage Enable Current (pins 6, 11)          | V <sub>en</sub> = L           |                        |            |            | -10        | μA       |

| I <sub>en</sub> = H | High Voltage Enable<br>Current (pins 6, 11)      | $V_{en}$ = H $\leq$ Vss –0.6V |                        |            | 30         | 100        | μA       |

| VCEsat (H)          | Source Saturation Voltage                        | l∟ = 1A<br>l∟ = 2A            |                        | 0.95       | 1.35<br>2  | 1.7<br>2.7 | V<br>V   |

| VCEsat (L)          | Sink Saturation Voltage                          | I∟ = 1A (5)<br>I∟ = 2A (5)    |                        | 0.85       | 1.2<br>1.7 | 1.6<br>2.3 | V<br>V   |

| V <sub>CEsat</sub>  | Total Drop                                       | I∟ = 1A (5)<br>I∟ = 2A (5)    |                        | 1.80       |            | 3.2<br>4.9 | V<br>V   |

| Vsens               | Sensing Voltage (pins 1, 15)                     |                               |                        | -1 (1)     |            | 2          | V        |

## **Application**

## 1、 POWER OUTPUT STAGE

The XBLW GT298 integrates two power output stages (A ; B). The power output stage is a bridge onfiguration and its outputs can drive an inductive load in common or differenzial mode, depending on the state of the inputs.

The current that flows through the load comes out from the bridge at the sense output : an external resistor (RSA; RSB.) allows to detect the intensity of this current.

### 2 、 INPUT STAGE

All the inputs are TTL compatible

### 3、 POWER

A non inductive capacitor, usually of 100 nF, must be foreseen between both Vs and Vss, to ground, as near as possible to GND pin.The en terminal shall be in L state before the output protection is turned off and on.

### 4 、 OUTPUT PROTECTION

The fast diode shall be selected as the output protection when driving inductive load. When I = 2 A, VF  $\leq$  1.2V, TRR  $\leq$  200 ns.

#### 5 、 PARALLEL CONNECTION

When the driving current is greater than 2A, two groups can be connected in parallel for current expansion.

## Package

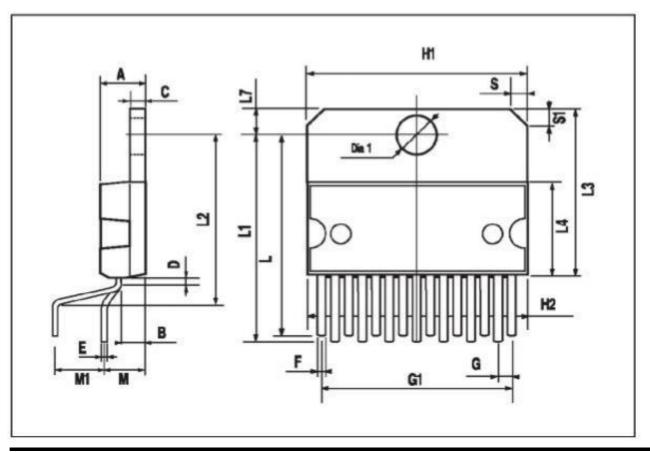

# Multiwatt15/ZIP-15

| DIM. | mm    |       |                   | inch  |       |       |

|------|-------|-------|-------------------|-------|-------|-------|

| DIW. | MIN.  | TYP.  | P. MAX. MIN. TYP. |       | MAX.  |       |

| Α    |       |       | 5                 |       |       | 0.197 |

| В    |       |       | 2.65              |       |       | 0.104 |

| С    |       |       | 1.6               |       |       | 0.063 |

| D    |       | 1     |                   |       | 0.039 |       |

| E    | 0.49  |       | 0.55              | 0.019 |       | 0.022 |

| F    | 0.66  |       | 0.75              | 0.026 |       | 0.030 |

| G    | 1.02  | 1.27  | 1.52              | 0.040 | 0.050 | 0.060 |

| G1   | 17.53 | 17.78 | 18.03             | 0.690 | 0.700 | 0.710 |

| H1   | 19.6  |       |                   | 0.772 |       |       |

| H2   |       |       | 20.2              |       |       | 0.795 |

| L    | 21.9  | 22.2  | 22.5              | 0.862 | 0.874 | 0.886 |

| L1   | 21.7  | 22.1  | 22.5              | 0.854 | 0.870 | 0.886 |

| L2   | 17.65 |       | 18.1              | 0.695 |       | 0.713 |

| L3   | 17.25 | 17.5  | 17.75             | 0.679 | 0.689 | 0.699 |

| L4   | 10.3  | 10.7  | 10.9              | 0.406 | 0.421 | 0.429 |

| L7   | 2.65  |       | 2.9               | 0.104 |       | 0.114 |

| М    | 4.25  | 4.55  | 4.85              | 0.167 | 0.179 | 0.191 |

| M1   | 4.63  | 5.08  | 5.53              | 0.182 | 0.200 | 0.218 |

| S    | 1.9   |       | 2.6               | 0.075 |       | 0.102 |

| S1   | 1.9   |       | 2.6               | 0.075 |       | 0.102 |

| Dia1 | 3,65  |       | 3.85              | 0.144 |       | 0.152 |

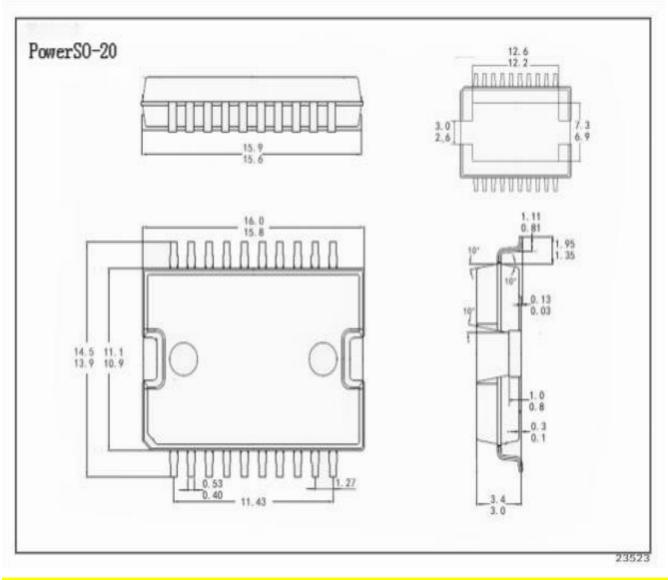

## PowerSO-20/HSOP-20

## **Declaration**

\* Shenzhen Xinbole Electronics Co., Ltd. reserves the right to modify the product manual without prior notice! Customers are advised to confirm if the information received is the latest version and verify the completeness of related information before placing an order.

\* Under certain conditions, any semiconductor product may fail or malfunction. It is the buyer's responsibility to comply with safety standards and take appropriate safety measures when designing systems and manufacturing complete machines using products from Shenzhen Xinbole Electronics Co., Ltd. to avoid potential risks of failure that may cause personal injury or property damage.

\* This document is for reference only, and the actual use should be based on the application test results.

Product performance improvement is endless. Shenzhen Xinbole Electronics Co., Ltd. will sincerely provide customers with integrated circuit products with better performance and higher quality.