3A,4.5V-16V Input,500kHz Synchronous Step-Down Converter

#### **FEATURES**

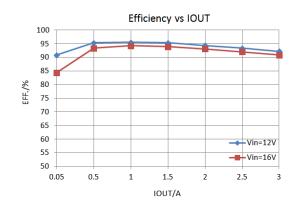

- High Efficiency: Up to 96%

- 500KHz Frequency Operation

- 3A Output Current

- No Schottky Diode Required

- 4.5V to 16V Input Voltage Range

- 0.6V Reference

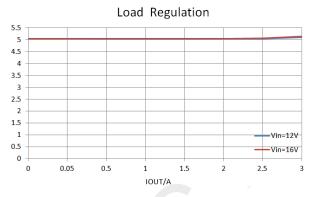

- Slope Compensated Current Mode Control for Excellent Line and Load Transient Response

- Integrated internal compensation

- Stable with Low ESR Ceramic Output Capacitors

- Over Current Protection with Hiccup-Mode

- Thermal Shutdown

- Inrush Current Limit and Soft Start

- Available in SOT23-6 Package

- -40°C to +85°C Temperature Range

# **APPLICATIONS**

- Distributed Power Systems

- Digital Set Top Boxes

- Flat Panel Television and Monitors

- Wireless and DSL Modems

- Notebook Computer

#### GENERAL DESCRIPTION

The SDA626 is a fully integrated, high—efficiency 3A synchronous rectified step-down converter. The SDA626 operates at high efficiency over a wide output current load range.

This device offers two operation modes, PWM control and PFM Mode switching control, which allows a high efficiency over the wider range of the load.

The SDA626 requires a minimum number of readily available standard external components and is available in an 6-pin SOT23 ROHS compliant package.

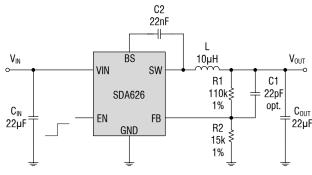

### TYPICAL APPLICATION

Figure 1. Basic Application Circuit

# ABSOLUTE MAXIMUM RATINGS(Note 1)

| Input Supply Voltage                      | 0.3V to 17V                          | Thermal Resistance θ <sub>JA</sub> 170°C/ | /W  |

|-------------------------------------------|--------------------------------------|-------------------------------------------|-----|

| EN Voltages                               | 0.3V to 17V                          | Junction Temperature(Note2)15             | 0°C |

| FB Voltages                               | 0.3V to 6V                           | Operating Temperature Range40°C to 85     | 5°C |

| SW Voltage                                | 0.3V to $(V_{IN} + 0.5V)$            | Lead Temperature(Soldering, 10s)300       | 0°C |

| BS Voltage                                | ( $V_{SW}$ -0.3V) to ( $V_{SW}$ +5V) | Storage Temperature Range65°C to 15       | 0°C |

| Power Dissipation                         | 0.6W                                 | ESD HBM(Human Body Mode)2                 | 2kV |

| Thermal Resistance $\theta_{\text{JC}}$ . | 130°C/W                              | ESD MM(Machine Mode)20                    | )0V |

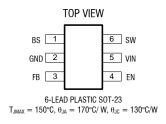

### **PACKAGE/ORDER INFORMATION**

# **PIN DESCRIPTION**

| Pin Name | Pin Number | Description                                                                                                                       |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------|

| BS       | 1          | Bootstrap. A capacitor connected between SW and BS pins is required to form a floating supply across the high-side switch driver. |

| GND      | 2          | Analog ground pin.                                                                                                                |

| FB       | 3          | Adjustable version feedback input. Connect FB to the center point of the external resistor divider.                               |

| EN       | 4          | Drive this pin to a logic-high to enable the IC. Drive to a logic-low to disable the IC and enter micro-power shutdown mode.      |

| VIN      | 5          | Power supply Pin                                                                                                                  |

| SW       | 6          | Switching Pin                                                                                                                     |

# **ELECTRICAL CHARACTERISTICS (Note 3)**

( $V_{IN}$ =12V,  $V_{OUT}$ =5V,  $T_A$  = 25°C, unless otherwise noted.)

| PARAMETER                           | CONDITIONS                                               | MIN   | TYP | MAX   | UNIT          |

|-------------------------------------|----------------------------------------------------------|-------|-----|-------|---------------|

| Input Voltage Range                 |                                                          | 3.3   |     | 16    | V             |

| Supply Current in Operation         | $V_{EN}$ =2.0V, $V_{FB}$ =1.1V                           |       | 0.4 | 0.6   | mA            |

| Supply Current in Shutdown          | $V_{EN} = 0$ or $EN = GND$                               |       | 1   |       | μΑ            |

| Regulated Feedback<br>Voltage       | $T_A = 25^{\circ}C, 4.5V \leqslant V_{IN} \leqslant 18V$ | 0.588 | 0.6 | 0.612 | ٧             |

| High-Side Switch On-Resistance      |                                                          |       | 80  |       | mΩ            |

| Low-Side Switch On-Resistance       |                                                          |       | 60  |       | mΩ            |

| High-Side Switch<br>Leakage Current | $V_{EN}$ =0V, $V_{SW}$ =0V                               |       | 0   | 10    | μΑ            |

| Upper Switch Current<br>Limit       | Minimum Duty Cycle                                       |       | 5   |       | А             |

| EN rising threshold                 |                                                          | 1.5   |     |       | V             |

| EN falling threshold                |                                                          |       |     | 0.4   | V             |

| Oscillation Frequency               |                                                          |       | 0.5 |       | MHz           |

| Maximum Duty Cycle                  | $V_{FB} = 0.6V$                                          |       | 92  |       | %             |

| Minimum On-Time                     |                                                          |       | 60  |       | nS            |

| Soft-start Time                     | Tss                                                      |       | 4   |       | mS            |

| Thermal Shutdown                    |                                                          |       | 160 |       | ${\mathbb C}$ |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:  $T_J = T_A + (P_D) x (170^{\circ}C/W)$ .

**Note 3**: 100% production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

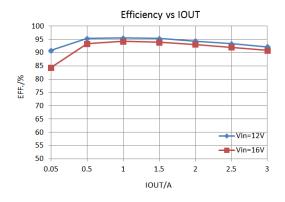

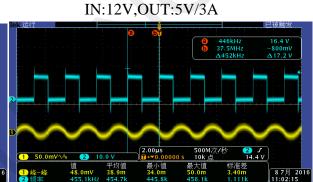

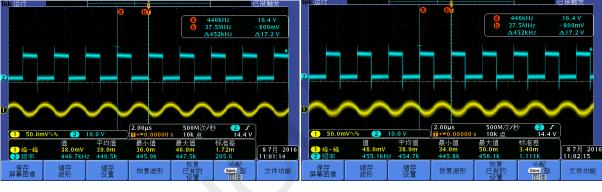

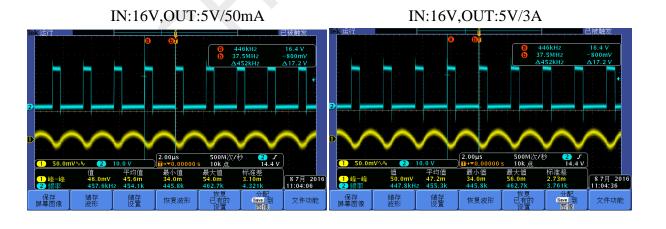

### TYPICAL PERFORMANCE CHARACTERISTICS

IN:12V,OUT:5V/50mA

www.sdw-tw.com SDA626 Rev1.0 4

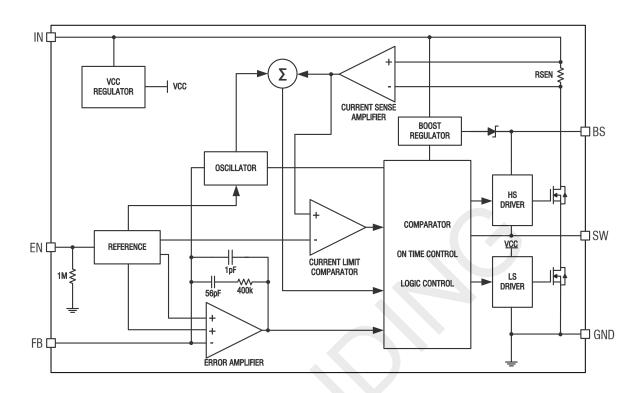

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SDA626 Block Diagram

### FUNCTIONAL DESCRIPTION

#### Internal Regulator

The SDA626 is a current mode step down DC/DC converter that provides excellent transient response with no extra external compensation components. This device contains an internal, low resistance, high voltage power MOSFET, and operates at a high 500K operating frequency to ensure a compact, high efficiency design with excellent AC and DC performance.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage with the internal FB reference ( $V_{\text{FB}}$ ) and outputs a current proportional to the difference between the two. This output current is then used to charge or discharge the internal compensation network to form the COMP voltage, which is used to control the power MOSFET current. The optimized internal compensation network minimizes the external component counts and simplifies the control loop design.

#### Internal Soft-Start

The soft-start is implemented to prevent the converter output voltage from overshooting during startup. When the chip starts, the internal circuitry generates a soft-start voltage (SS) ramping up from 0V to 0.6V. When it is lower than the internal reference (REF), SS overrides REF so the error amplifier uses SS as the reference. When SS is higher than REF, REF regains control. The SS time is internally fixed to 4 ms.

#### Over-Current-Protection and Hiccup

The SDA626 has cycle-by-cycle over current limit when the inductor current peak value exceeds the set current limit threshold. Meanwhile, output voltage starts to drop until FB is below the Under-Voltage (UV) threshold, typically 30% below the reference. Once a UV is triggered, the SDA626 enters hiccup mode to periodically restart the part. This protection mode is especially useful when the output is dead-short to ground. The average short circuit current is greatly reduced to alleviate the thermal issue and to protect the regulator. The SDA626 exits the hiccup mode once the over current condition is removed.

#### Startup and Shutdown

If both VIN and EN are higher than their appropriate thresholds, the chip starts. The reference block starts first, generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides stable supply for the remaining circuitries. Three events can shut down the chip: EN low, VIN low and thermal shutdown. In the shutdown procedure, the signaling path is first blocked to avoid any fault triggering. The COMP voltage and the internal supply rail are then pulled down. The floating driver is not subject to this shutdown command.

### APPLICATIONS INFORMATION

#### **Setting the Output Voltage**

The external resistor divider is used to set the output voltage (see Typical Application on page 1). The feedback resistor R1 also sets the feedback loop bandwidth with the internal compensation capacitor. Choose R1 to be around  $100k\Omega$  for optimal transient response. R2 is then given by:

$$R2 = \frac{R1}{\frac{V_{out}}{V_{fR}} - 1}$$

### **Inductor Selection**

A  $4.7\mu H$  to  $22\mu H$  inductor with a DC current rating of at least 25% percent higher than the maximum load current is recommended for most applications. For highest efficiency, the inductor DC resistance should be less than  $15m\Omega$ . For most designs, the inductance value can be derived from the following equation.

$$L = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times \Delta I_{\text{L}} \times f_{\text{OSC}}}$$

Where  $\triangle$  I<sub>L</sub> is the inductor ripple current. Choose inductor ripple current to be approximately 30% if the maximum load current, 3A. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency.

#### **Input Capacitor Selection**

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency should be less than input source impedance to prevent high frequency switching current passing to the input. A low ESR input capacitor sized for maximum RMS current must be used. Ceramic capacitors

with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A  $22\mu$ F ceramic capacitor for most applications is sufficient. A large value may be used for improved input voltage filtering.

#### **Output Capacitor Selection**

The output capacitor  $(C_{\text{OUT}})$  is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times f_{\text{OSC}} \times L} \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{OSC}} \times C_{\text{OUT}}}\right)$$

Where L is the inductor value and  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor. In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_{\text{OSC}}^2 \times L \times C_{\text{OUT}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{OSC}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times R_{\text{ESR}}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The SDA626 can be optimized for a wide range of capacitance and ESR values.

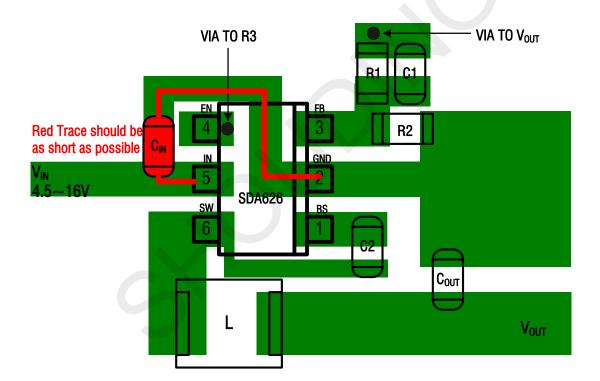

#### **PCB Layout Recommendations**

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for optimum performance. If change is necessary, please follow these guidelines and take Figure 3 for reference.

- Keep the path of switching current short and minimize the loop area formed by Input capacitor, high-side MOSFET and low-side MOSFET.

- Bypass ceramic capacitors are suggested to be put close to the VIN Pin.

- Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- ➤ V<sub>OUT</sub>, SW away from sensitive analog areas such as FB.

- Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

- ➤ An example of 2-layer PCB layout is shown in Figure 3 for reference.

Figure 3. SDA626 Suggested Layout

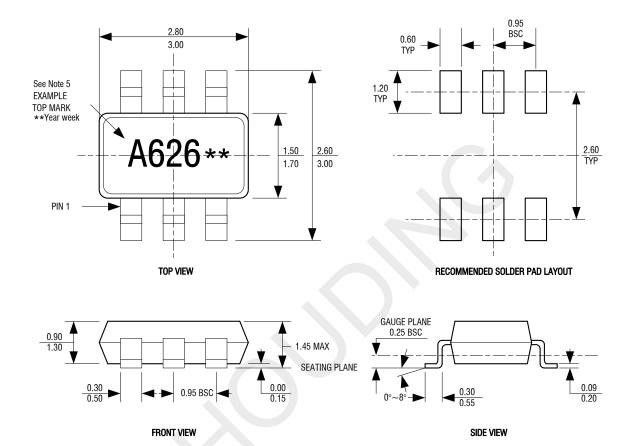

# **PACKAGE DESCRIPTION**

#### S0T23-6

- NOTE:

1.DIMENSIONS ARE IN MILLIMETERS.

2.DRAWING NOT TO SCALE.

3.DIMENSIONS ARE INCLUSIVE OF PLATING.

4.DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR.

5.PIN 1IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

www.sdw-tw.com SDA626 Rev1.0 9